## Brief Introduction of Cell-based Design

Ching-Da Chan CIC/DSD

www.narlabs.org.tw

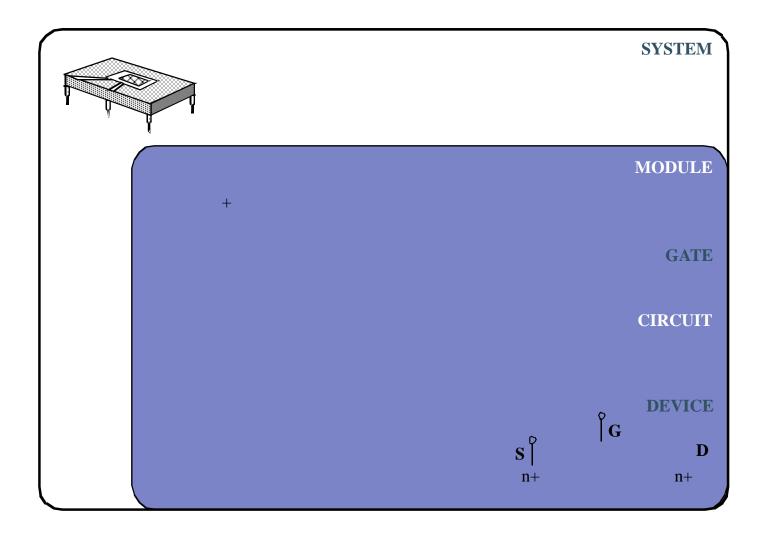

#### **Design Abstraction Levels**

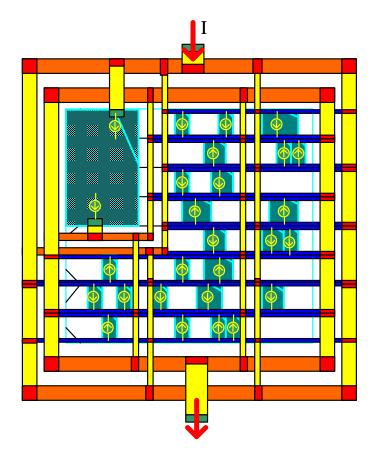

## Full Custom V.S Cell based Design

- Full custom design

- Better patent protection

- Lower power consumption

- Smaller area

- More flexibility

| والمسجور فيعاف فالتكر المحجر ومساولا إزار |  |           |

|-------------------------------------------|--|-----------|

|                                           |  | <u>91</u> |

|                                           |  | Щ.        |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  | - 2       |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

|                                           |  |           |

#### NARLabs Full Custom V.S Cell based Design (cont.)

- Cell-based design

- Less design time

- Easer to implement large system

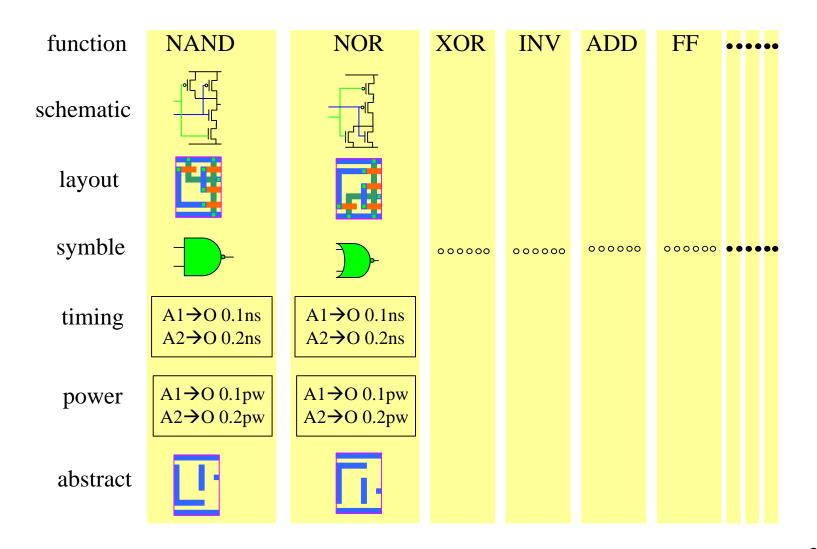

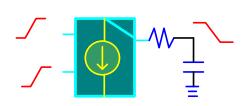

## Prepare Standard Cell Library

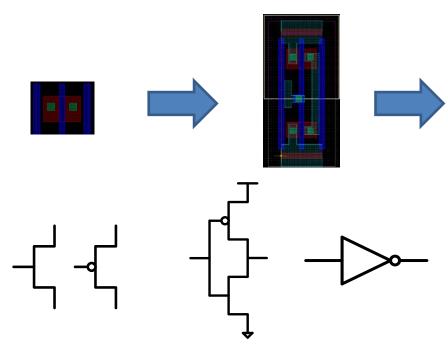

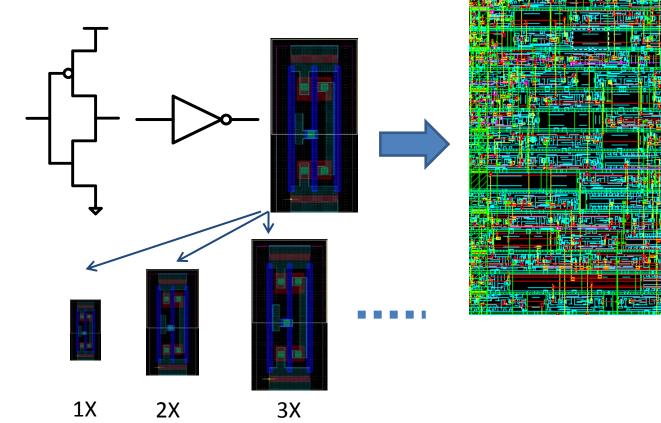

- 1. Circuit design

- Equal height but different width.

- Cell unit is unit tile(ex. 2X, 3X, 4X...).

- 2. Cell Characterization

- Characterize all condition of input signal.

- Extraction the cell view(abstract)

#### NARLabs

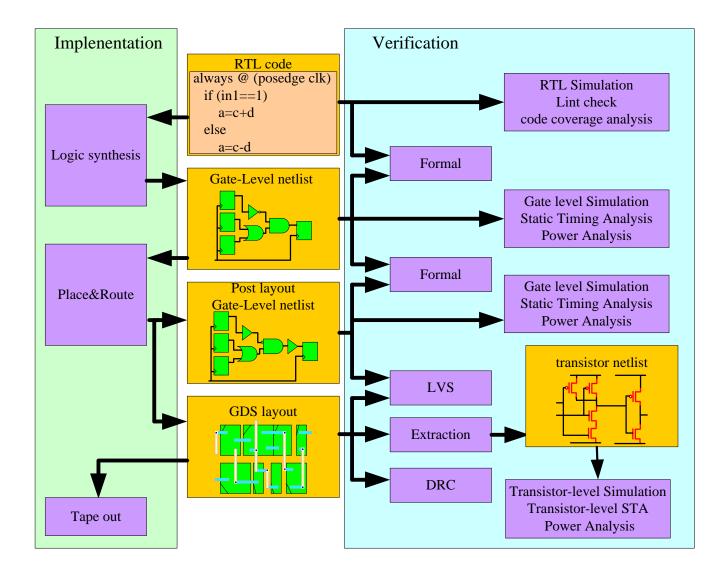

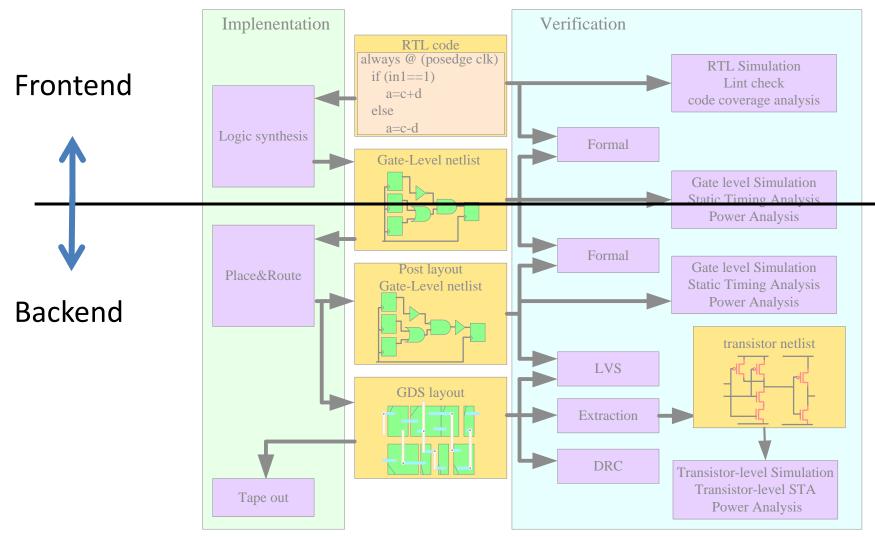

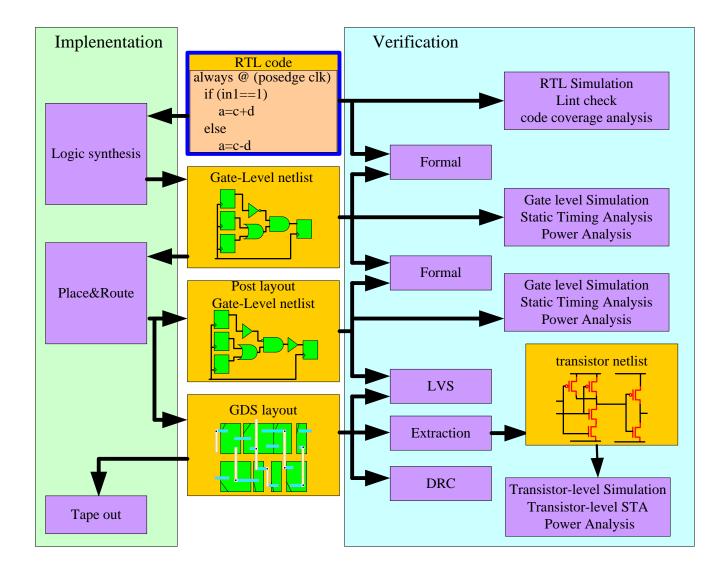

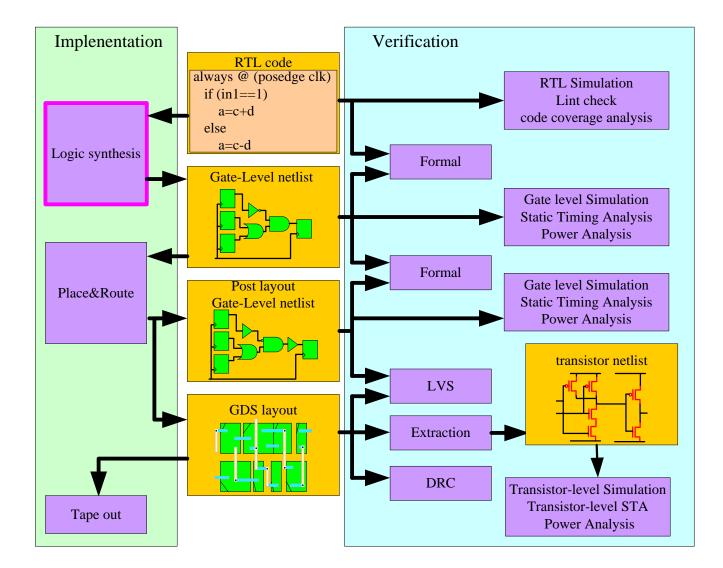

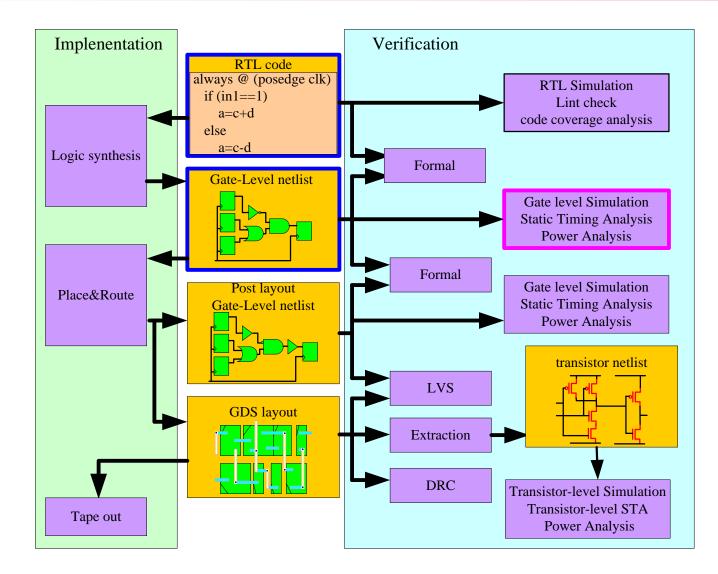

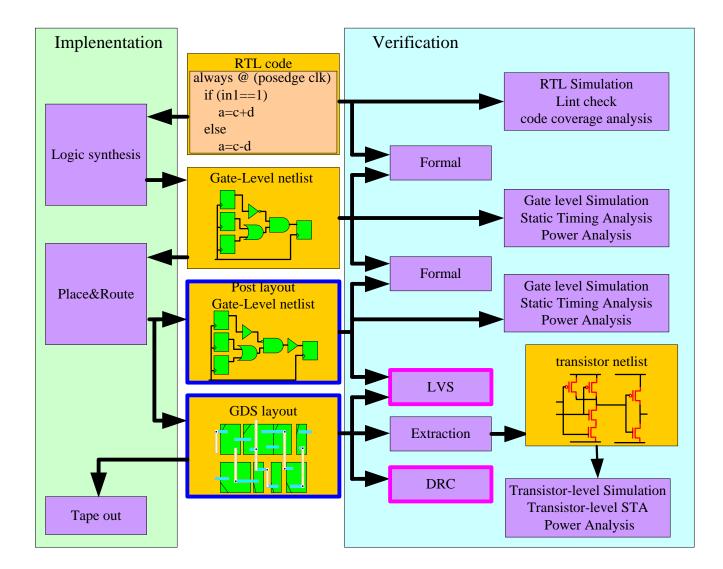

#### Cell-Based IC Design Flow Overview

### **General Design Process**

Idea Design Verification Implementation Verification Verification Implementation

Verified Chip Layout

...

#### **NARLabs** Cell-Based IC Design Flow Overview

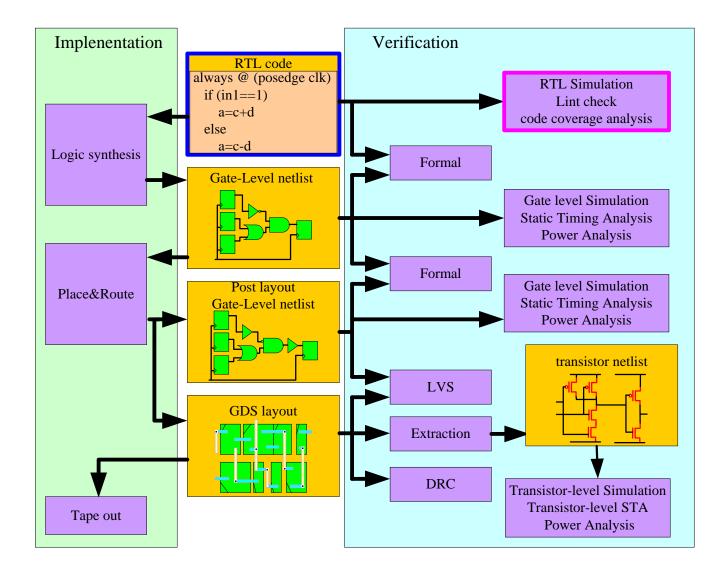

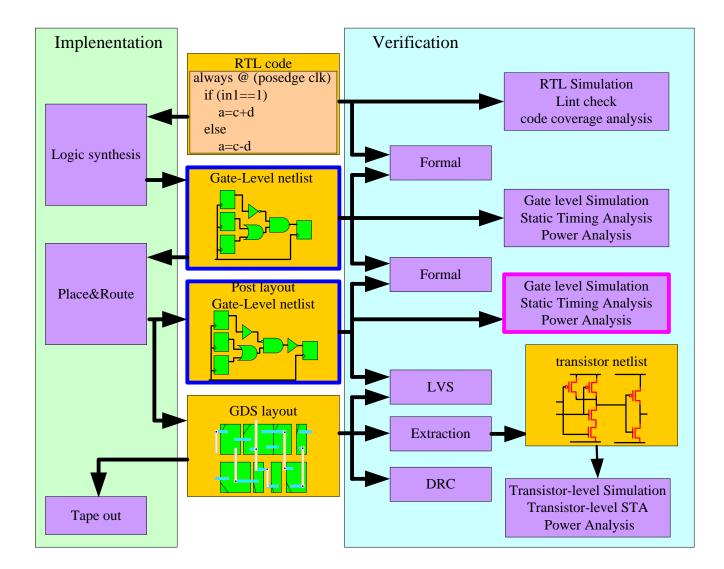

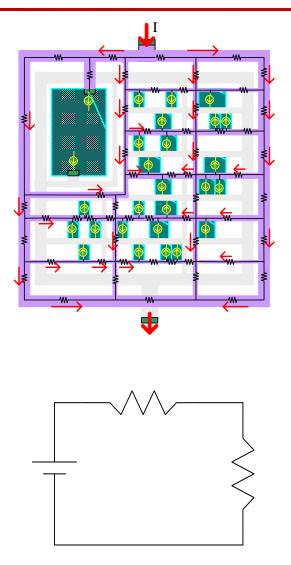

## Partition of Design Flow

- Front end

- System specification and architecture

- ─ ■DL coding & behavioral simulation

- Synthesis & gate level simulation

- Back end

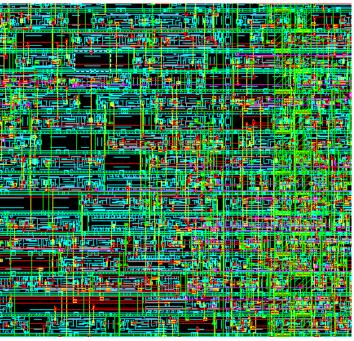

- Placement and routing

- DRC (Design Rule Check), LVS (Layout vs Schematic)

- *<sup>†</sup> indication inditation inditation indication*

## Cell-Based IC Design Flow - RTL Design

#### NARLabs Specification of Design Example

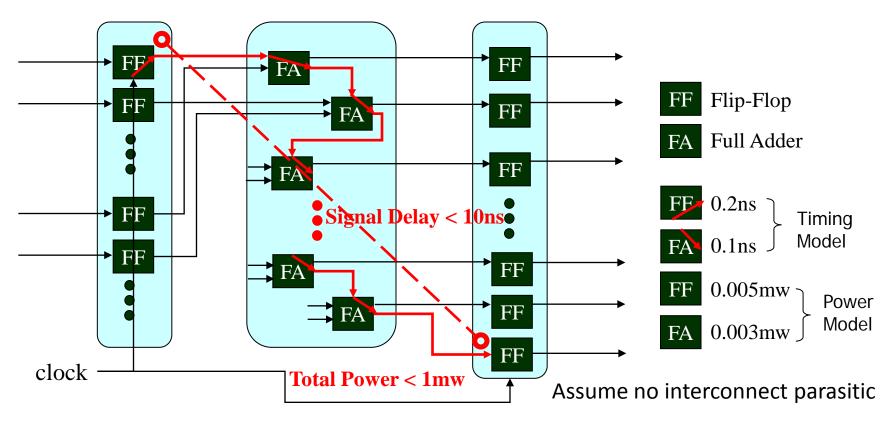

- Design Example Specification

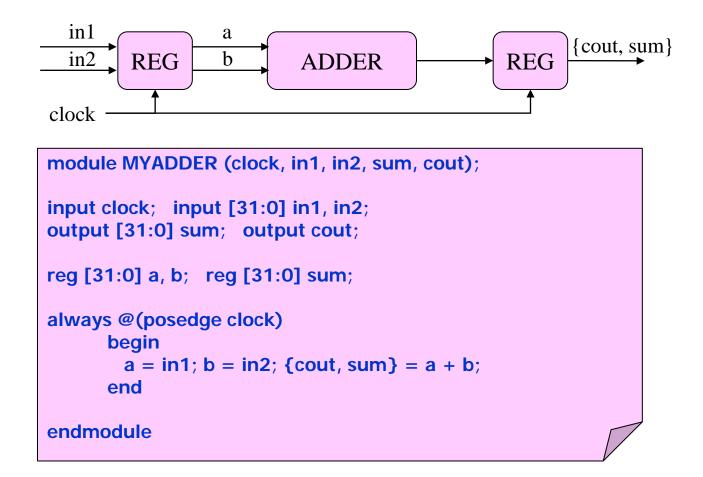

- Two 32-bit unsigned integer inputs are captured at the positive clock edge and the sum outputs at the following positive edge clock edge

- 32-bit unsigned integer inputs means input data Types

- Positive clock edge means input or output spec.

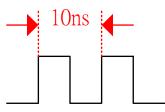

- The clock period is 10ns

- Clock period is the distance of two clock edge.

- 10ns means the data must calculate finished at 10ns

- The power consumption should be less than 1mw

### **RTL HDL Coding**

• RTL = Register Transfer Level

## **Basic Building Block: Modules**

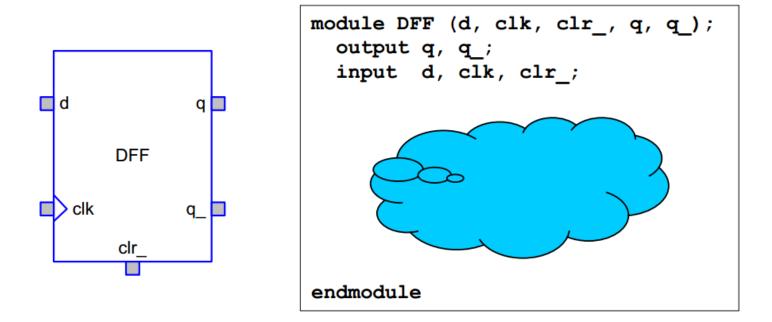

- Modules are the basic building blocks.

- Descriptions of circuit are placed inside modules.

- Modules can represent:

- A physical block (ex. standard cell)

- A logic block (ex. ALU portion of a CPU design)

- The complete system

- Every module description starts with the keyword module, followed by a name, and ends with the keyword endmodule.

#### **NARLabs** Communication Interface: Module Ports

- Modules communicate with the outside world through ports.

- Module port types can be: input, output or inout(bidirectional)

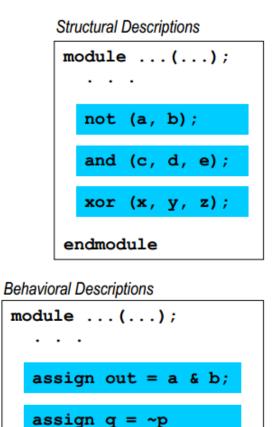

#### **NARLabs** What's Inside the Module?

endmodule

| Behavioral Descriptions         |  |

|---------------------------------|--|

| <pre>module();</pre>            |  |

| always @()<br>begin             |  |

| end                             |  |

| always @()<br>begin             |  |

| end                             |  |

| <pre>initial @()    begin</pre> |  |

| end                             |  |

| endmodule                       |  |

Deberieral Descriptions

**Mixed Descriptions**

| <pre>module();   </pre>         |  |

|---------------------------------|--|

| and (a, b, c);                  |  |

| assign out = a & b;             |  |

| always @()<br>begin             |  |

| end                             |  |

| <pre>initial @()    begin</pre> |  |

| end                             |  |

| endmodule                       |  |

#### NARLabs

## Verilog Basis & Primitive Cell Supported

- Verilog Basis

- parameter declarations

- wire, wand, wor declarations

- reg declarations

- input, ouput, inout declarations

- continuous assignments

- module instantiations

- gate instantiations

- always blocks

- task statements

- function definitions

- for, while loop

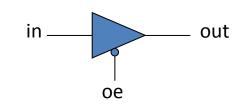

- Synthesizable Verilog primitives cells

- and, or, not, nand, nor, xor, xnor

- bufif0, bufif1, notif0, notif1

## HDL Compiler Unsupported

- delay

- initial

- repeat

- wait

- fork ... join

- event

- deassign

- force

- release

- primitive -- User defined primitive

- time

- triand, trior, tri1, tri0, trireg

- nmos, pmos, cmos, rnmos, rpmos, rcmos

- pullup, pulldown

- rtran, tranif0, tranif1, rtranif0, rtranif1

example: wire out=(!oe)? in : 'hz;

NARLabs

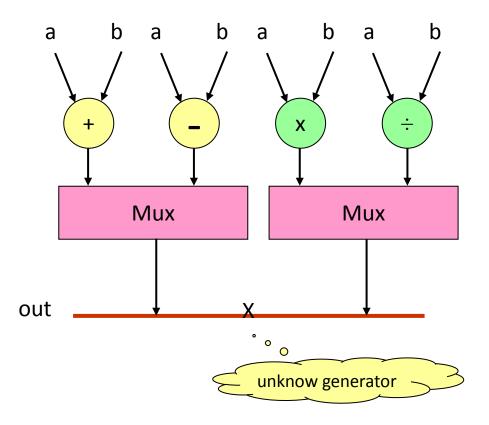

#### Example for Error always syntax

```

module top(clk, a, b, out, ...);

output out;

input a, b, clk;

reg

out;

@(posedge clk)begin

always

if(en1)

out=a+b;

else

out=a-b;

end

@(posedge clk)begin

always

if(en2)

out=a*b;

else

out=a/b;

end

:

endmodule

```

#### Synthesis Unsupported

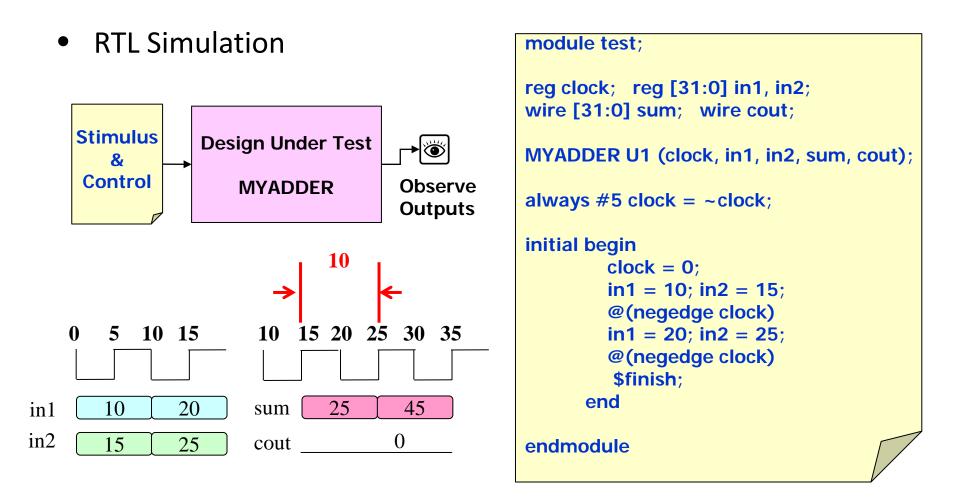

### **RTL** Verification

## **RTL Verification**

#### Cell-Based IC Design Flow - Logic Synthesis

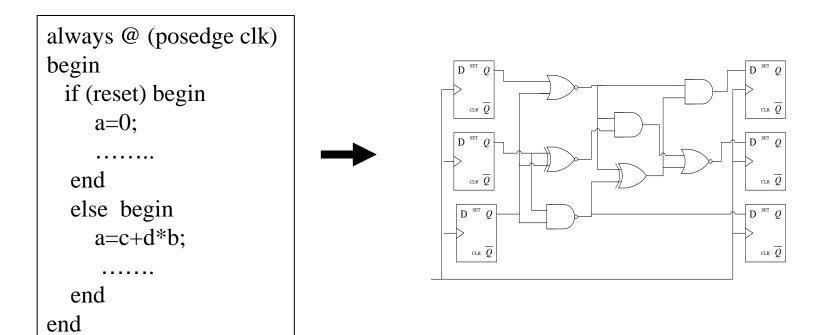

### Logic Implementation

- Logic Synthesis

- Design for Testability (DFT)

- Memory BIST

- Scan Insertion

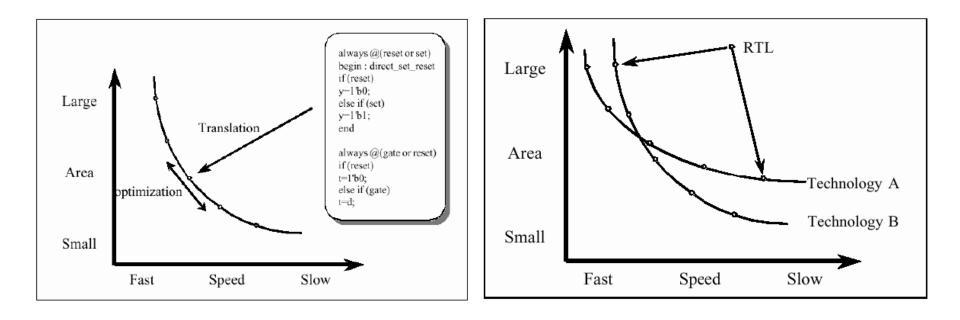

#### NARLabs What is Synthesis? (1/2)

•Synthesis = translation + optimization

#### **NARLabs** What is Synthesis? (2/2)

# Synthesis is constraint drivenTechnology independent

## Logic Synthesis

Map RTL HDL to Gate-level Synthesizable RTL HDL HDL according to the design constraints and environment Translation **Timing Constraints** Architecture Opt. Area Constraints **Design Constraints** Power Constraints **Design Rule Constraints Generic Boolean Operating Conditions Design Environment** Wire Load Model System Interface **Technology Mapping** AND Logic Opt. OR **INVERTER Cell Library** FLIP-FLOP **Gate-level HDL ADDER**

## **Cell Library**

## **Design Example**

- Translation: Ripple Adder

- Technology Mapping: Meet timing & power constraints

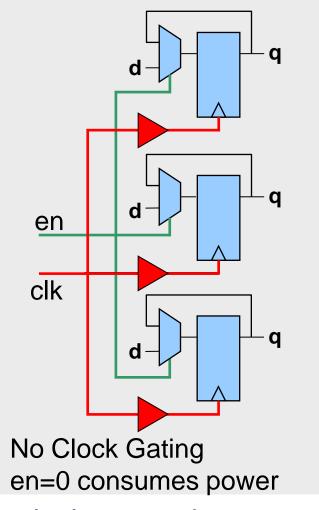

#### **Clock Gating Reduces Both Power and Area**

Clock gate reduces switching activity on the clock tree

### **Clock Gating Coding Style**

| If statement              | always@ (posedge clk)<br>if (enable) Q <= D_in;                                                         |  |

|---------------------------|---------------------------------------------------------------------------------------------------------|--|

| lf + Loop<br>statement    | <pre>always @ (posedge clk) if (enable) for (i=0; i&lt;8; i=i+1) s[i] = a[i] ^ b[i];</pre>              |  |

| Conditional<br>Assignment | <pre>always@ (posedge clk)   Q &lt;=(enable)? D_in : Q;</pre>                                           |  |

| Case<br>statement         | <pre>always@ (posedge clk)   case (enable)     1'b1: Q &lt;= D_in;     1'b0: Q &lt;= Q;   endcase</pre> |  |

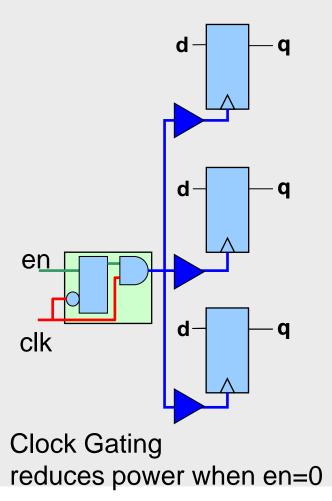

- Provide a shorthand way of writing a series of statements

- In synthesis, for loops loops are "<u>unrolled</u>", and then synthesized

- Example

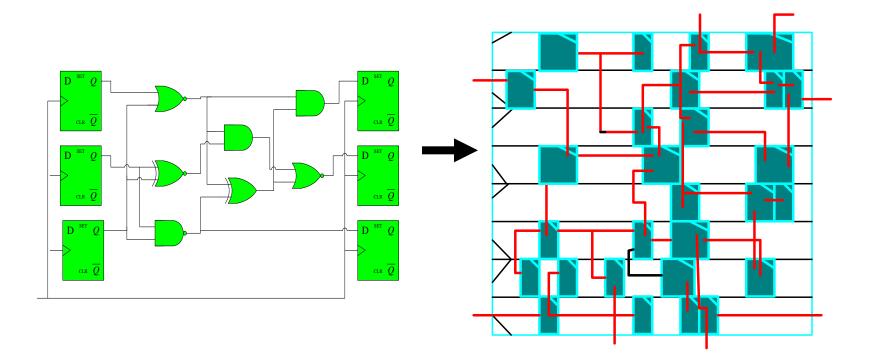

### Netlist after Synthesis

. . .

#### • RTL

```

end

```

endmodule

#### • Gate Level

module MYADDER (clock, in1, in2, sum, cout);

```

input clock; input [31:0] in1, in2;

output [31:0] sum; output cout;

```

```

DFCNQD1 11_ (.CP (cki), .D (n_22));

MOAI22D0 g301.A2 (ck_down_12_));

IND2D1 g300 (ck_down_13_), .ZN (n_25));

DFCNQD1 ck_down_reg_12_(.D (n_24));

MOAI22D0

```

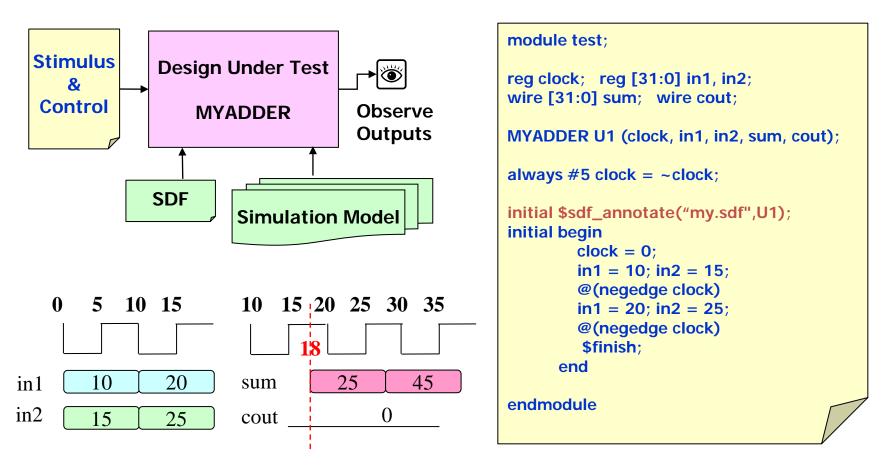

#### **NARLabs** Pre-layout Gate-level Verification

## Pre-layout Gate-level Verification

- Function Verification

- Pre-layout Gate-level Simulation

- Timing Verification

- Pre-layout Gate-level Simulation

- Pre-layout Static Timing Analysis (STA)

- Power Verification

- Power Analysis

#### **NARLabs** Pre-layout Gate-level Simulation

• SDF: Standard Delay Format

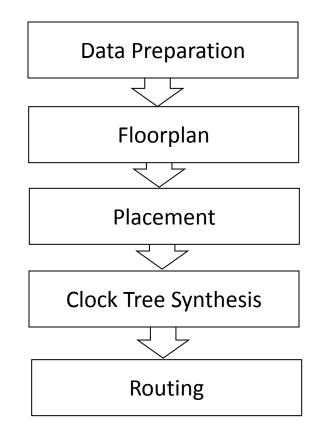

## Cell-Based IC Design Flow - Place & Route

#### **Physical Implementation**

### **Physical Implementation**

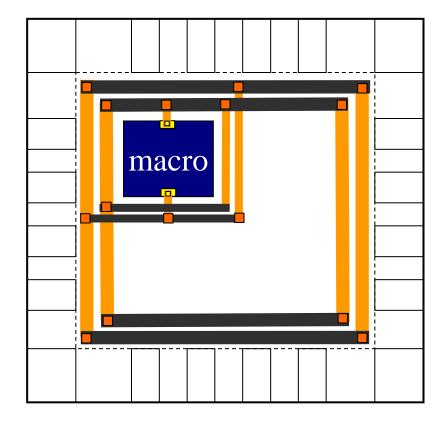

#### **Data Preparation**

- Verified Pre-layout Gate-level HDL

- Timing/Power Constraints

- Similar to those for logic synthesis

- Layout Constraints

- Chip Size / Aspect Ratio / IO Constraints

- Physical Partitions (Region / Group)

- Macro Positions...

- Cell Libraries

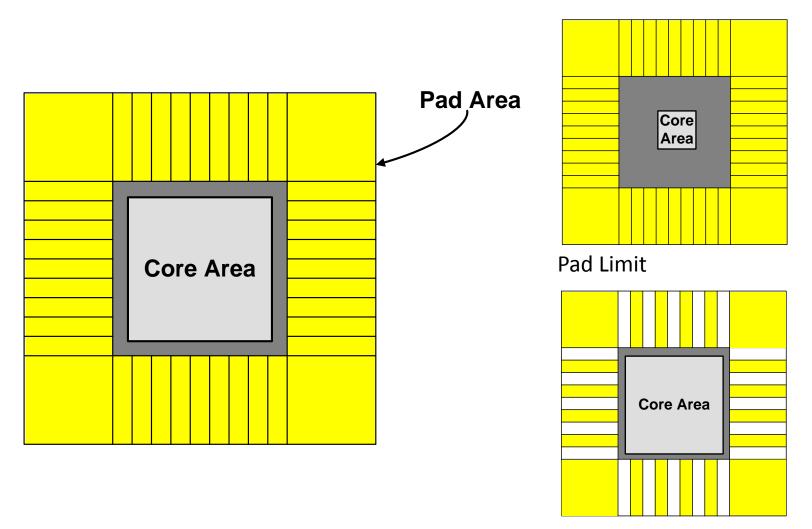

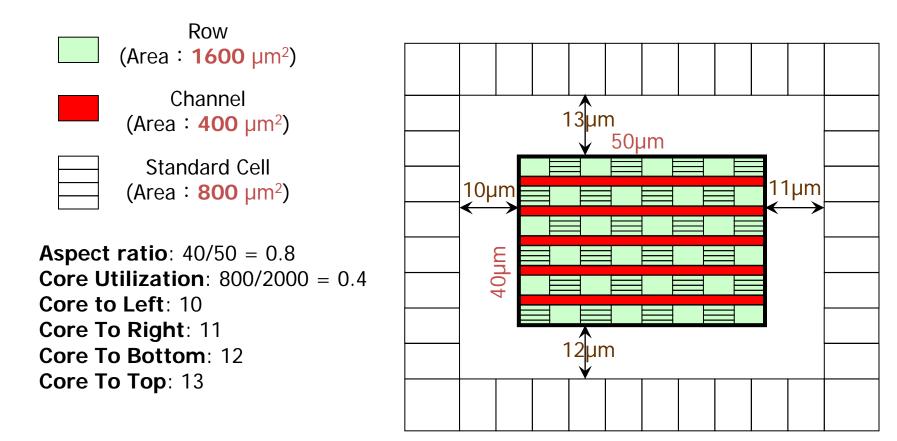

## Floorplan Area

Core Limit

#### **Floorplan - Parameters**

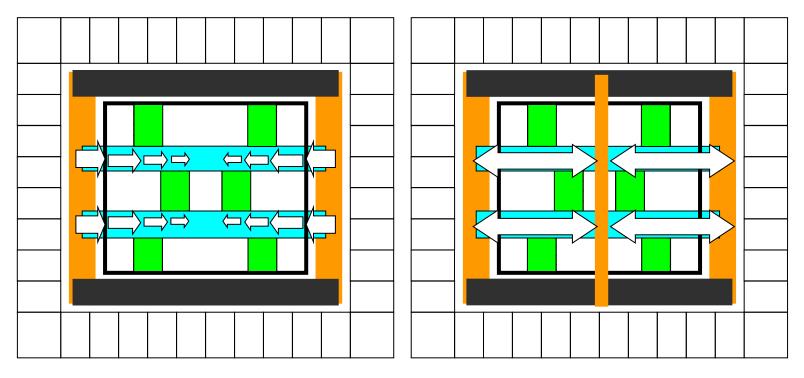

#### **NARLabs** Floorplan - Power Mesh (Ring)

#### **NARLabs** Floorplan - Power Mesh (Strap)

without strap (or stripe)

with strap (or stripe)

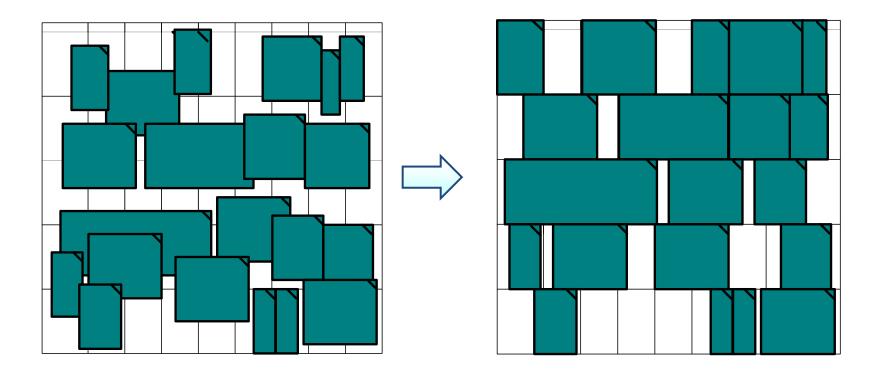

•Timing driven

Congestion driven

#### **Timing-Driven Placement**

Timing-driven placement tries to place cell along timingcritical path close together to reduce net RCs and meet setup timing

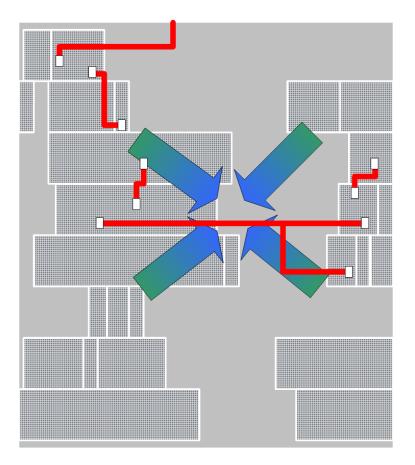

#### Understanding the Congestion Calculation

#### NARLabs

Congestion

hot spot

**Congestion Map**

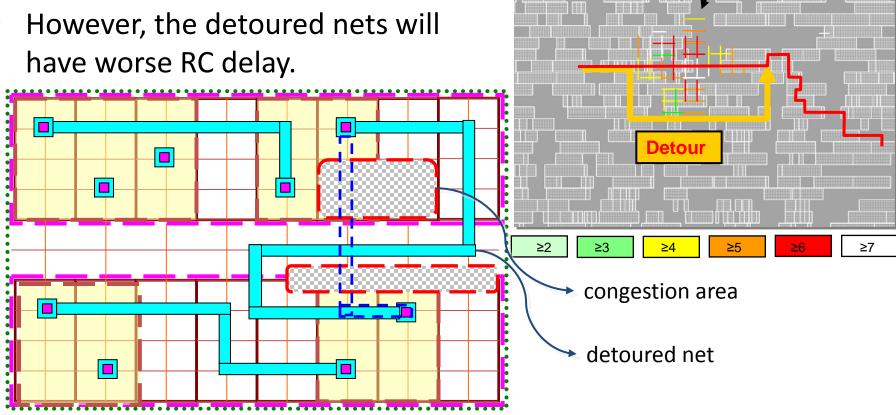

## One Problem with Congestion...

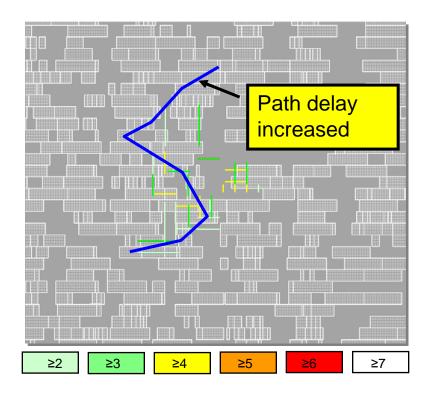

- If congestion is not too severe, the actual route can be detoured around the congested area

- However, the detoured nets will have worse RC delay.

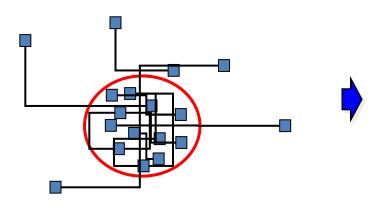

#### **NARLabs** What does Congestion-Driven Placement do?

Spreads apart cells that contribute to high congestion.

## What happens to timing when the connected cells are moved apart?

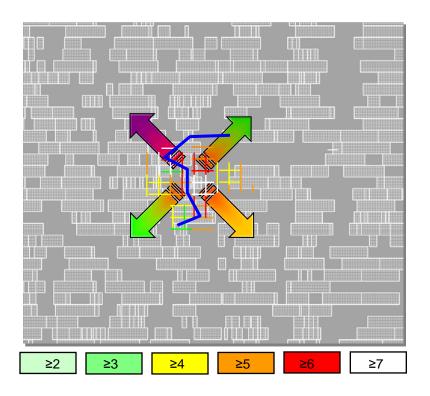

#### **NARLabs** Congestion vs. Timing Driven Placement

- Cells along timing critical paths can be spread apart to reduce congestion

- These paths <u>may</u> now violate timing

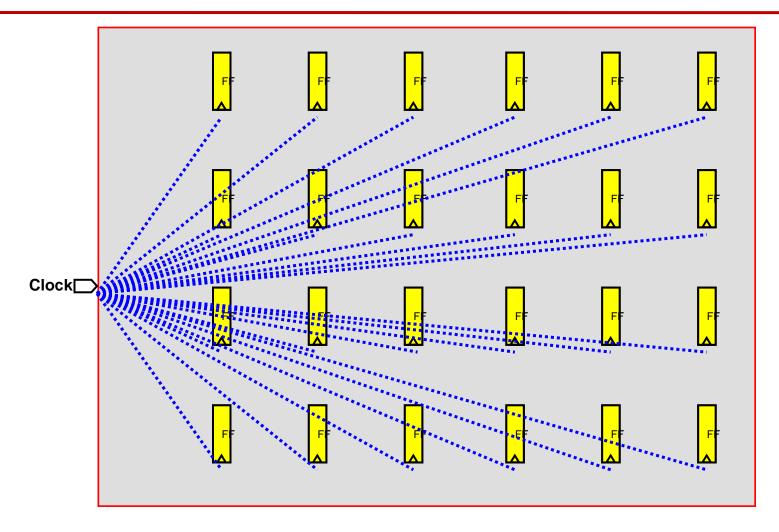

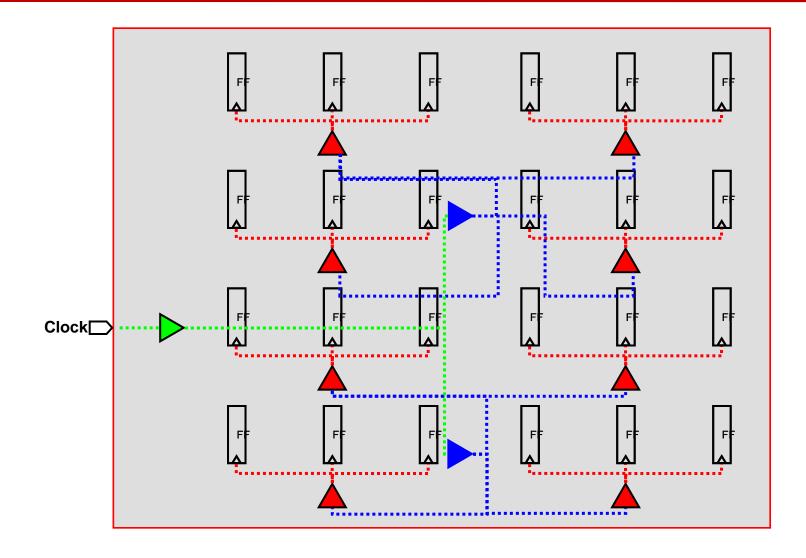

#### Starting Point before CTS

All clock pins are driven by a single clock source.

#### **CTS for Design Example**

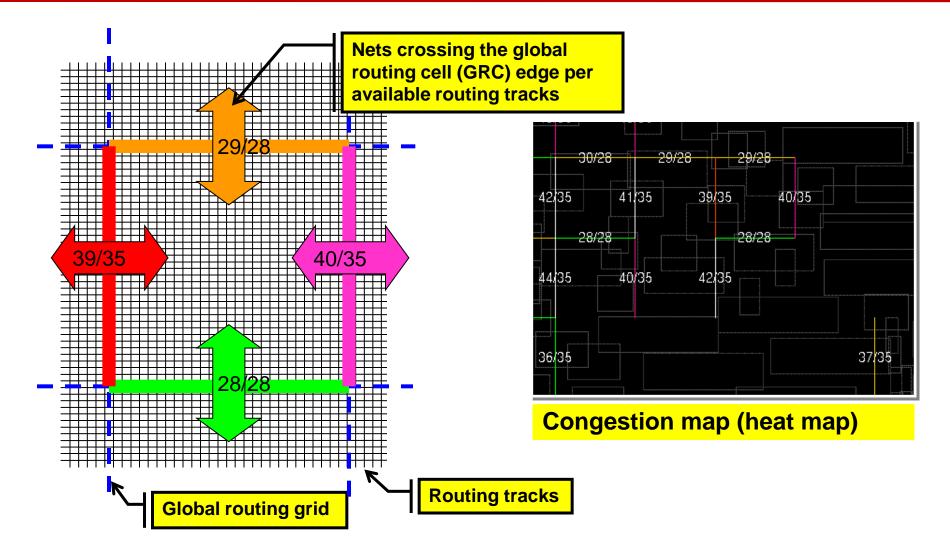

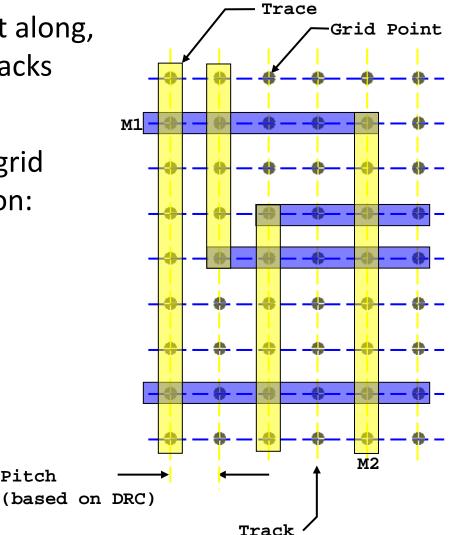

## **Grid-based Routing System**

Pitch

- Metal traces (routes) are built along, and centered upon routing tracks based on a grid.

- Each metal layer has its own grid and preferred routing direction:

- > VHV

- M1: Vertical

- M2: Horizontal, etc...

- ► HVH

- M1: Horizontal

- M2: Vertical, etc...

• After three stage all of the net connection with metal.

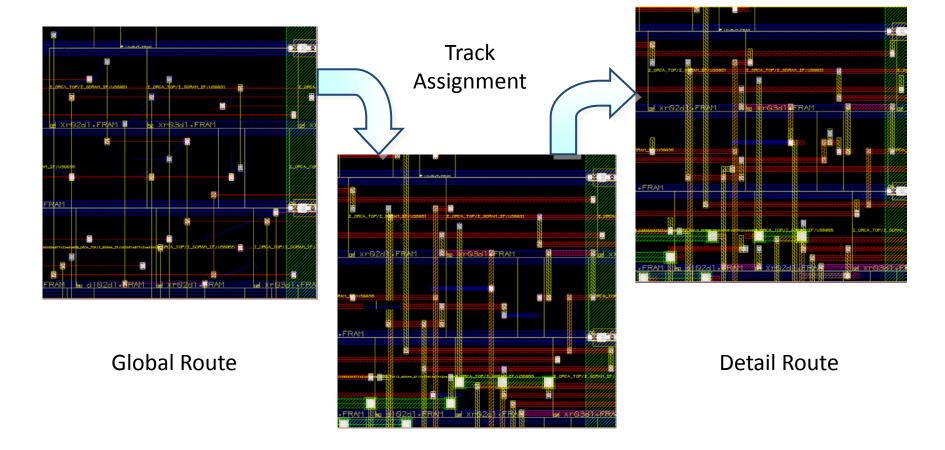

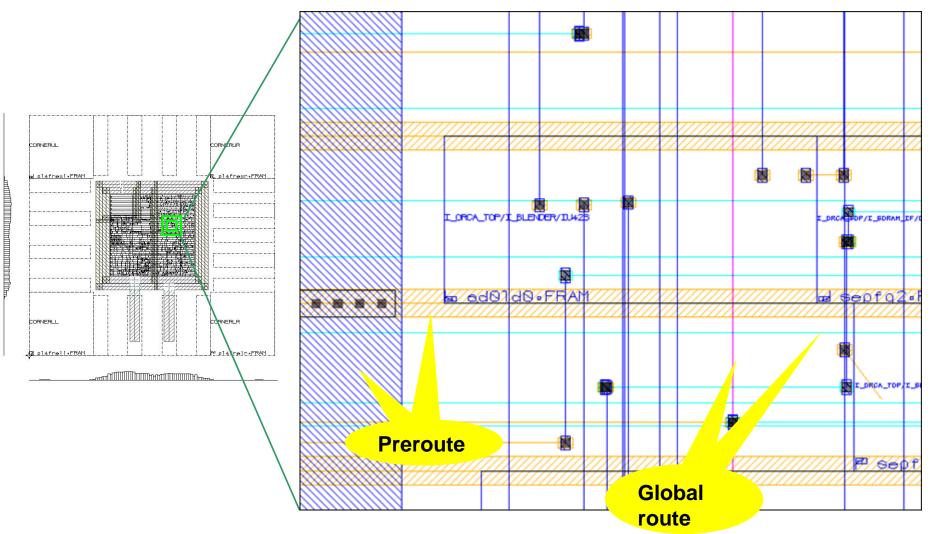

#### **Routing - Global Route**

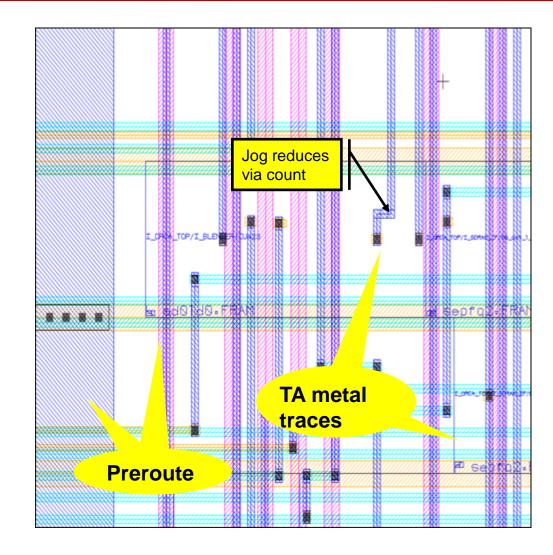

#### **Routing - Track Assignment**

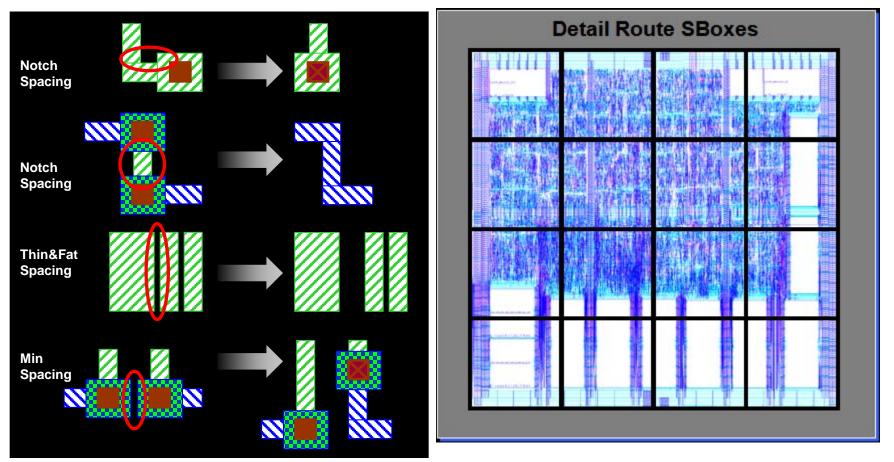

#### **Routing - Detail Route**

Detail route attempts to clear DRC violations using a fixed size Sbox

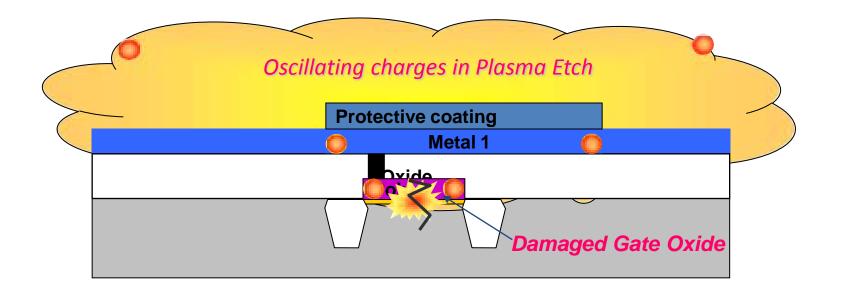

## DFM Problem: Gate Oxide Integrity

- Metal wires (antennae) placed in an EM field generate voltage gradients

- During the metal etch stage, strong EM fields are used to ionize the plasma etchant

#### NARLabs

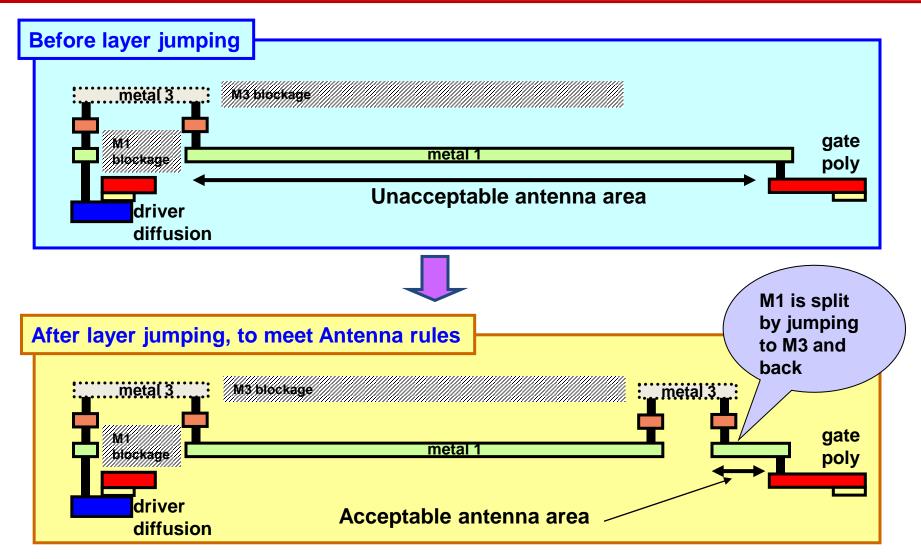

### Solution 1: Splitting Metal or Layer Jumping

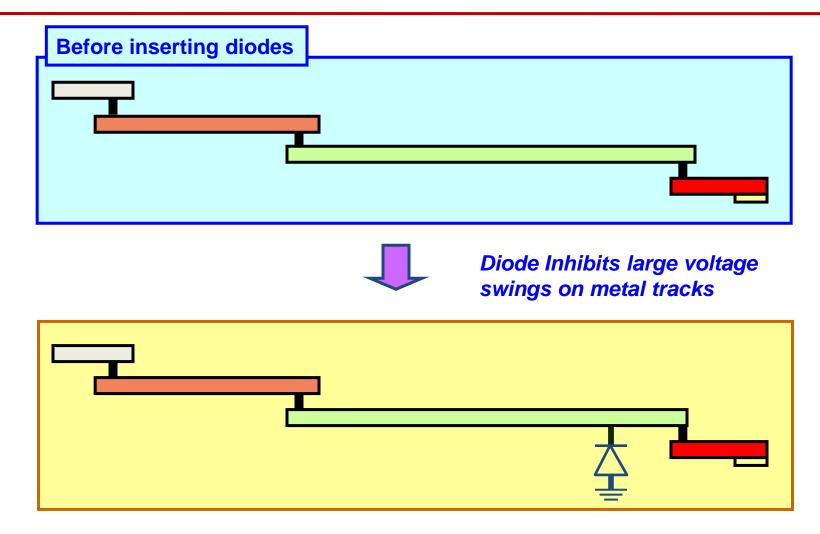

#### **Solution 2: Inserting Diodes**

During etch phase, the diode clamps the voltage swings.

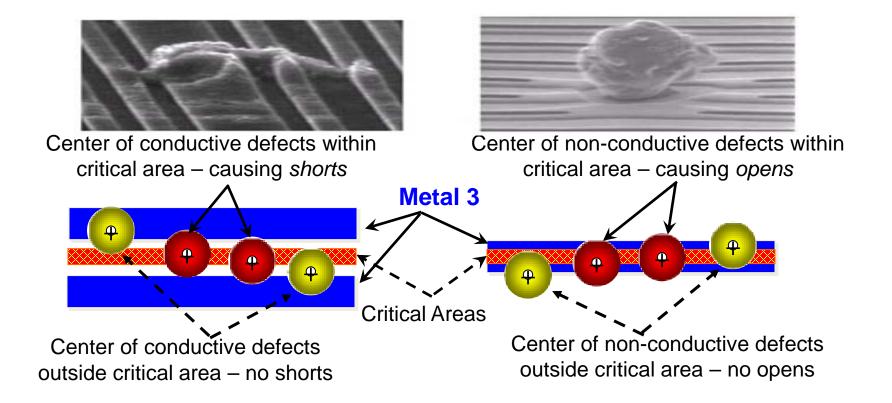

#### **NARLabs** DFM Problem: Random Particle Defects

Random particle defects during manufacturing may cause shorts or opens during the fabrication process

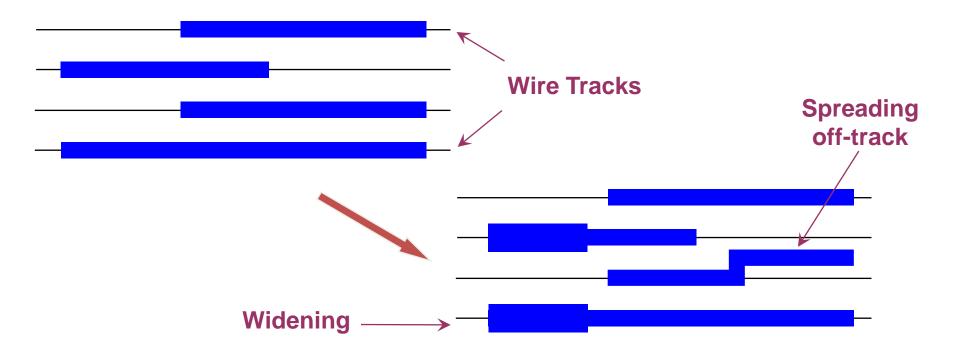

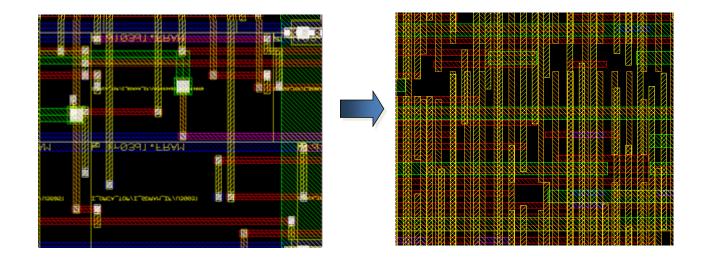

#### **NARLabs** Solution: Wire Spreading + Widening

- Spread wires to reduce *short* critical area

- Widen wires to reduce open critical area

## Voids in Vias during Manufacturing

- Voids in vias is a serious issue in manufacturing

- Two solutions are available:

- Reduce via count:

- > Add backup vias: known as redundant vias

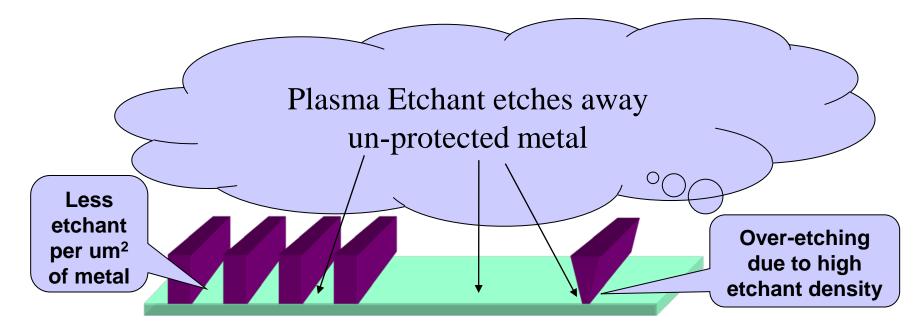

## **Problem: Metal Over-Etching**

- A metal wire in low metal density region receives a higher ratio of etchant can get over-etched

- <u>Minimum</u> metal density rules are used to control this

• Fills empty tracks on all layers (default) with metal shapes to meet the minimum metal density rules

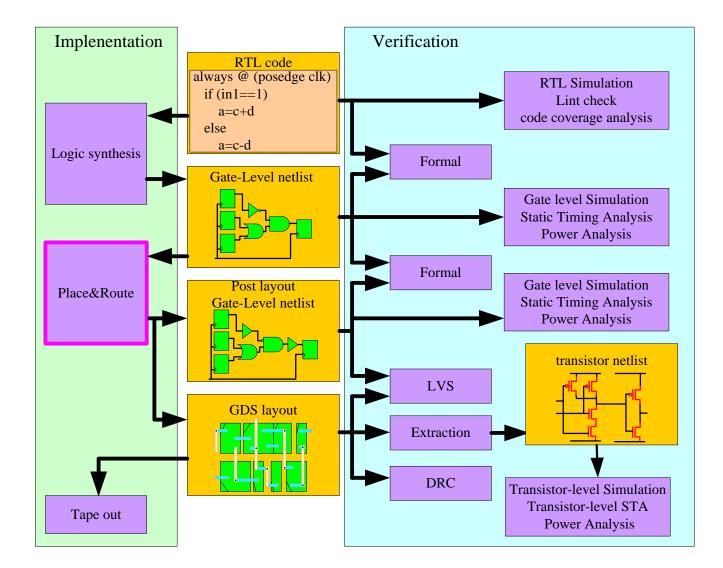

# Cell-Based IC Design Flow

#### - Post-layout Verification

## NARLabs Post-layout Gate-level Verification

#### • Function Verification

- Post-layout Gate-level Simulation

- Formal Equivalence Checking

- Pre-layout Gate-level HDL vs. Post-layout Gate-level HDL

- Timing Verification

- Post-layout Gate-level Simulation

- Post-layout Static Timing Analysis (STA)

- Power Verification

- Power Analysis

Estimated Interconnect Parasitic => Real Interconnect Parasitic

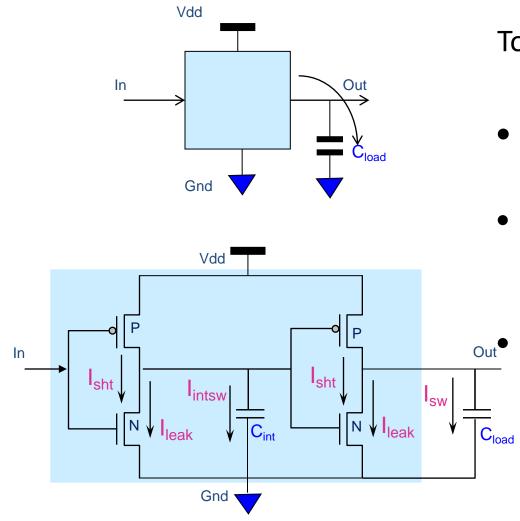

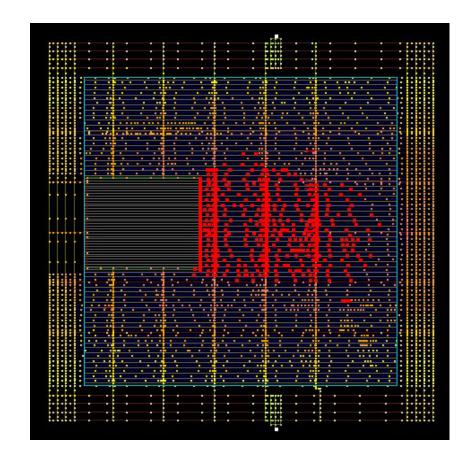

#### **Power Analysis**

Total Power=

Dynamic Power + Static Power

- Switching power (dynamic):

- Charging output load

- Internal power (dynamic)

- Short circuit

- Charging internal load

- Leakage power (static)

- Stable state

#### **Power Analysis**

#### **Rail Analysis**

IR power graph

#### NARLabs

#### Cell-Based IC Design Flow - Physical Verification

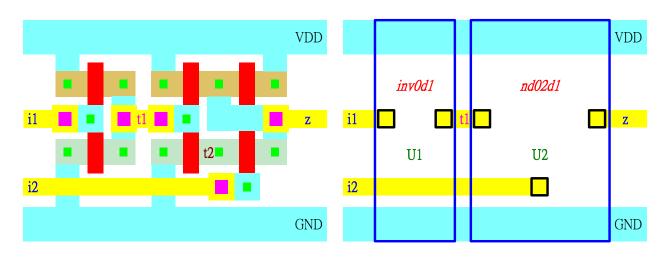

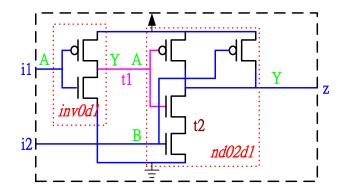

## **Physical Verification**

- For geometrical verification

- Design Rule Check (DRC)

- For topological verification

- Layout versus Schematic (LVS)

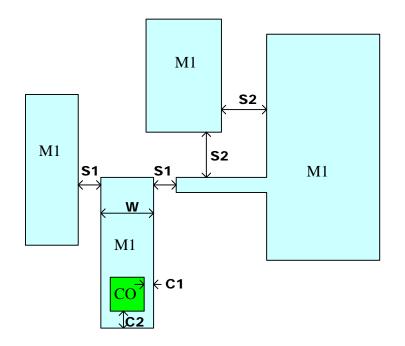

#### **Design Rule Check**

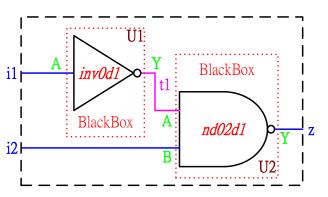

#### Black Box LVS

LVS

**Black-box LVS**

## THE END